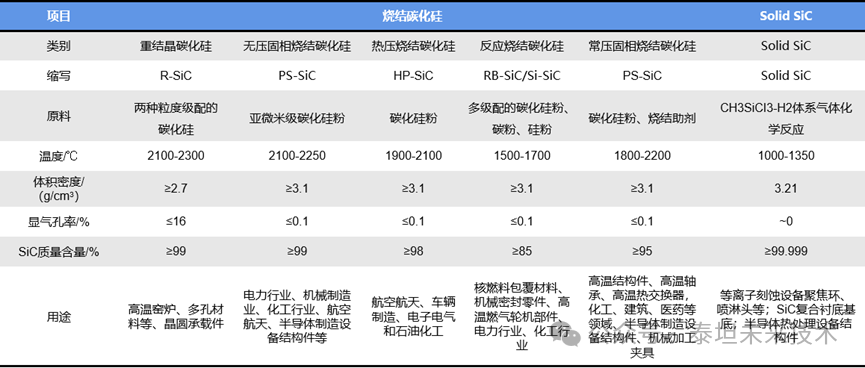

Solid SiC又称实体碳化硅或固体碳化硅,是采用化学气相沉积(CVD)法将化学反应生成的碳化硅材料沉积在基材上,并形成一定的形状。然后根据具体用途,采取特定方法将碳化硅材料从基材上剥离下来,再将剥离下来的碳化硅材料进一步机械加工以满足最终使用需求。

Solid SiC作为一种高性能的材料,具备超高纯度、高耐腐蚀性、高耐氧化性、高耐热性、高耐磨损性的特性,具有与硅相似的电导率、良好的耐离子刻蚀性能,在外延、刻蚀工艺环节已经有极其重要的应用。

Solid SiC本质上是已经从基材上剥离下来的厚度约为1-20mm的SiC涂层块体,而不再是仅约100um的较薄的涂层。同时,Solid SiC与烧结SiC也有本质区别,应用范围各不相同。

SiC复合衬底技术

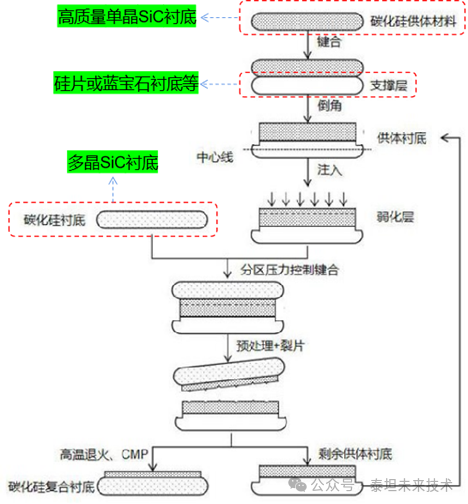

值得注意的是,随着新能源碳化硅产业的不断发展,对SiC衬底降本增效的需求越发急迫。据YOLE于2022年发布的SiC技术及市场研报,彼时SiC复合衬底技术刚刚展露头角,国际上仅有法国Soitec、日本住友金属子公司Sicoxs在着手进行产业化,直到2023年中国青禾晶圆也建成了首期SiC复合衬底产线。SiC复合衬底技术相比现有PVT技术能节约近10%的成本,而SiC复合衬底技术需要用到Poly Solid SiC Wafer作为原材料,SiC复合衬底技术将对Solid SiC有巨量需求。

在SiC复合衬底技术中,高质量单晶SiC供体晶圆的薄层被分离并粘合到低电阻率多晶SiC晶圆上,由此产生的SiC复合衬底可提高器件性能、成本、制造良率,该工艺允许对单个高质量单晶SiC供体晶圆进行多次重复使用。高质量SiC单晶衬底即PVT法制造出来的4H-SiC衬底,价格昂贵。而多晶SiC衬底则是CVD法沉积出来的3C-SiC(Solid SiC材质),价格相对便宜。

如今,高质量4H-SiC衬底的可用性仍然是行业的一个具有挑战性的限制,导致交货时间长和成本高。但根据Soitec的说法,在SiC复合衬底技术中,该高质量4H-SiC衬底供体晶圆至少可以使用十次。

SiC复合衬底的优势

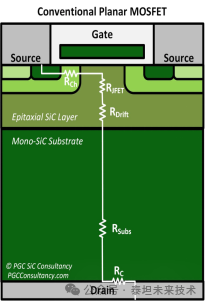

对于导电型SiC器件而言,导通电阻Rds,on越低越好。在MOSFET电阻构成的五个部分中(Rds,on=Rdrift+Rch+Rsubs+RJFET+Rc),尽管衬底厚度(6英寸为350um,8英寸为500um)远大于其余部分,但其电阻Rsubs仅占20%不到,衬底厚度对总导通电阻的影响极其有限;漂移区厚度(750V MOSFET,SiC外延层6-8um)占比很小,但其电阻Rdrift却占了60%,故而导电型SiC器件的耐压能力基本由SiC外延层厚度决定。

因此,SiC衬底厚度除了支撑作用,材料的利用率并不高,甚至6英寸衬底随后还会被减薄到100-180um,然后再沉积漏极金属触点,从而最大限度地减少衬底电阻的贡献。SiC复合衬底技术则很好的解决了这个问题。

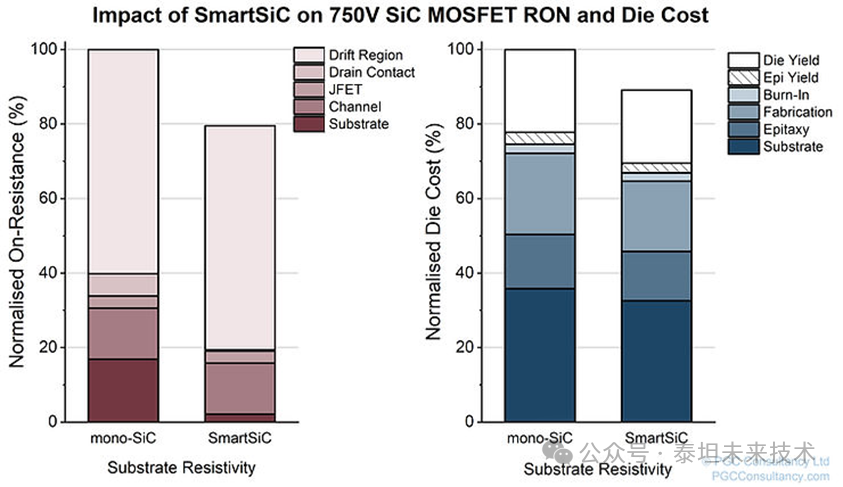

一方面,传统PVT法单晶SiC衬底的晶体质量(低缺陷密度)和掺杂密度(低电阻率)之间存在基本的权衡。由于衬底需要作为后续外延生长的基础,因此衬底的质量不能受到影响,其电阻往往相对较高。相反,在生产Poly Solid SiC衬底时,其缺陷密度则相对要求不高,因此其掺杂密度可以被推到极限,从而最小化其电阻。另一方面,传统PVT法单晶SiC衬底可以被重复利用,只有极薄的一层薄膜会留在每片复合衬底上作为外延层的高质量基底存在,材料利用率大大提高。

Soitec公司SmartSiC工艺的资料显示,750V SiC MOSFET的总器件电阻x面积(Ron.A)将减少20%。考虑到缩放芯片时的热效应,这意味着芯片尺寸减小了9.1%。较小的芯片增加了每个晶圆的芯片产量,成品芯片成本降低了10.9%。当对1200V SiC MOSFET进行相同的分析时,由于需要更厚、掺杂更低的漂移区域来支持更高的电压,因此衬底电阻的影响被稀释了。因此,SmartSiC衬底将器件的Ron.A降低了14.2%,相当于芯片成本降低了8.4%。

总的来说,SiC复合衬底技术不是现有PVT法的全面替代,传统PVT法高质量单晶SiC衬底仍然需要作为SiC复合衬底技术的原材料使用,但是由于SiC衬底利用率大大提升因此会冲击现有SiC衬底市场。同时,由于每生产1片SiC复合衬底都需要1片Poly Solid SiC Wafer作为原材料,SiC复合衬底技术的进一步商业化会利好Poly Solid SiC Wafer市场,并带动Poly Solid SiC Wafer的产业化。

SiC复合衬底生产厂家

拥有世界上最大的SOI晶圆(200毫米至300毫米)工业生产基地。2021年Soitec Smartsic工艺细节首次出现,并宣布与mersen合作研发新的poly sic平台。2022年3月Bernin4 fab工厂动工,2024年开始量产,计划2028年时年产50万片复合SiC衬底。2022年5月发布首款8寸Smartsic衬底,宣布和ST合作,在18个月内进行晶圆认证。2024年5月宣布与X-fab合作提供SmartSiC晶圆。2024年5月宣布与Tokai Carbon(东海炭素,其Solid SiC业务全球领先)建立战略合作伙伴关系,为Soitec SmartSiC晶圆开发多晶碳化硅衬底。东海炭素株式会社正在加紧将其开发的多晶SiC晶圆材料商业化,并宣布将投资54亿日元,在神奈川县茅崎市建立1条专用生产线,预计2024年12月完工。

成立于2012年6月,现为日本住友金属子公司。其目标是实现基于原创理念的新型半导体衬底。

2017年开始建设一条用于直接键合 SiC 衬底的原型量产线,目前正在向客户销售这些衬底的样品。2022年7月住友金属矿业株式会社宣布,其子公司Sicoxs将开建新的8寸SiC生产线,预计2024年3月完工,预计2025年加上现有的6寸SiC生产线,年产能合计达12万片。

成立于2020年7月,聚焦于新型半导体材料的研发生产制造,是全球少数掌握全套先进半导体材料与异质集成技术的半导体公司之一。

2023 年5月工厂通线,首期3万片/年6英寸SiC复合衬底。2024年4月宣布在SiC键合衬底的研发上取得重要进展,在国内率先成功制备了8英寸SiC键合衬底。2024年7月宣布完成超3亿元B轮融资,该轮融资将被用于先进键合设备及键合衬底产线建设。青禾晶元规划继续扩大生产规模,先进键合设备年产能将扩大至60台(套),以满足日益增长的客户需求,新建40万片8英寸SiC键合衬底产线,加速8英寸SiC衬底量产进程,进一步加强青禾晶元在国内键合集成技术领域的竞争优势。